|

|

|

Домашняя страничка

RA4HJW |

| Обновлено 9 декабря 2004г. |

|

Микроконтроллеры

Часто при подключении к контроллеру, при большом количестве функциональных узлов, возникает проблема с недостачей линий портов. В этом случай и используется данная схемка, изображенная на рис.1 для подключения ЖКИ-модуля на базе контроллера HD44780 к микро-ЭВМ семейства MCS-51. Режим работы с внешней памятью осуществляется по командам: MOVX A, @DPTR или MOVX A, @DPTR с обменом информацией по шине данных. Модуль индикации подключается к соответствующим контактам R/W, RS, E. Сигналы -RD, -WR непосредственно к контроллеру, CS1 - ИНСТРУКЦИИ, CS0 - ДАННЫЕ для HD44780 снимается с дешифратора устройств, собранном на любой микросхемке типа ИД3, ИД4, ИД7 серии 555 или подобной.

Фрагмент программы на MCS-51 MACRO ASSEMBLER, V2.2 приведен ниже

|

Большой популярностью у специалистов пользуются алфавитно-цифровые ЖКИ-модули на базе контроллера HD44780 фирмы Hitachi или его аналогов производства других фирм: Epson, Philips, Samsung, Sanyo, Toshiba . Контроллер HD44780 допускает подключение к микропроцессорам по четырёх битному или восьми битному интерфейсу. Выбор интерфейса производится пользователем исходя из ограничений на время, затрачиваемое на обмен данными с котроллером, или количество используемых линий подключения к микро-ЭВМ.

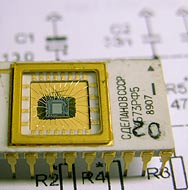

К572ПВ1 это двенадцатиразрядный АЦП имеет выходные каскады с тремя

состояниями (0, 1 и высокоимпедансное), благодаря чему может выдавать

информацию на системную шину микроконтроллера. Более того, кодовые выводы

АЦП могут использоваться не только для вывода, но и для ввода дискретных

сигналов, т.е. этот АЦП имеет двунаправленный кодовый канал. Возможность

записать внешний код в выходной регистр позволяет использовать данную

микросхему в качестве цифро-аналогового преобразователя.

Отклики писать на адрес внизу.

|

|

|

|

|

E-mail: ra4hjw@mail.ru © 2003-2016